検索

Contact

LVDS設定時の注意点

CX-Card5搭載のCyclone V FPGAデバイスでI/OピンをLVDS設定する際の注意点

アルテラ開発ツールQuartus Primeで、I/OピンをLVDS設定する場合には、Assinment Editorを利用するか、サンプルプロジェクトのCX-Card5.tclスクリプトを利用できます。

※ QuartusのPin Plannerだけでは詳細な設定ができません。

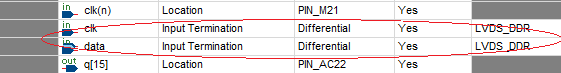

QuartusのAssignment Editorの場合、該当ピン(入力)の I/O StandardをLVDS設定するだけでは、オンチップの終端抵抗が適用されません。 必ず、該当ピンにINPUT TERMINATION Differentialを設定して下さい。

TCLスクリプトを利用してピン設定等を行う場合には、ピン番号アサインの他に以下の記述を追加して下さい。

set_instance_assignment -name IO_STANDARD LVDS -to 信号名

set_instance_assignment -name INPUT_TERMINATION DIFFERENTIAL -to 信号名