検索

Contact

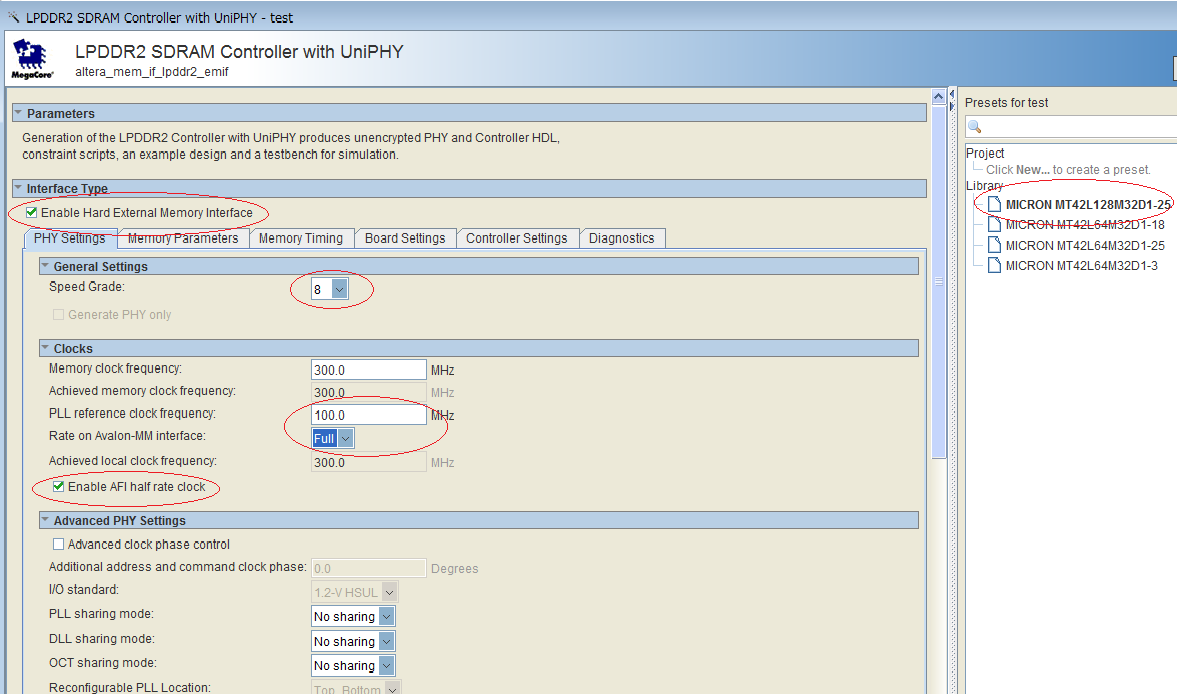

LPDDR2 IP設定

Quartsu2開発ツールでのLPDDR2制御IP設定方法

アルテラQuartus2開発ツール(v14.1以上)のIP Catalog欄から、Memory Interface with UniPHY を選択し、LPDDR2 SDRAM Controller with UniPHYをクリックします。

表示された設定画面を次のように変更します。

- 画面右から LPDDR2 型番の ”MT42L128M32D1-25”を選択

- Enable Hard External Memory Interfaceをチェック

- Speed Gradeを8に変更

- PLL reference clock frequencyを100MHzに変更

- Enable AFI half rate clockをチェック

これだけ変更したら、Finishボタンをクリックして制御コアを生成します。

LPDDR2制御コアを生成すると、xxxx_pin_assignments.tcl ファイルも自動生成されています。

製品添付のサンプルFPGAプロジェクトで提供しているFPGAピンアサイン用のTCLを実行してピンアサインした後、上記のxxxx_pin_assignments.tcl を実行すると、LPDDR2インタフェース用のピン定義が正しくできます。