アルテラQuartus2開発ツール(v14.1以上)のIP Catalog欄から、Memory Interface with UniPHY を選択し、LPDDR2 SDRAM Controller with UniPHYをクリックします。

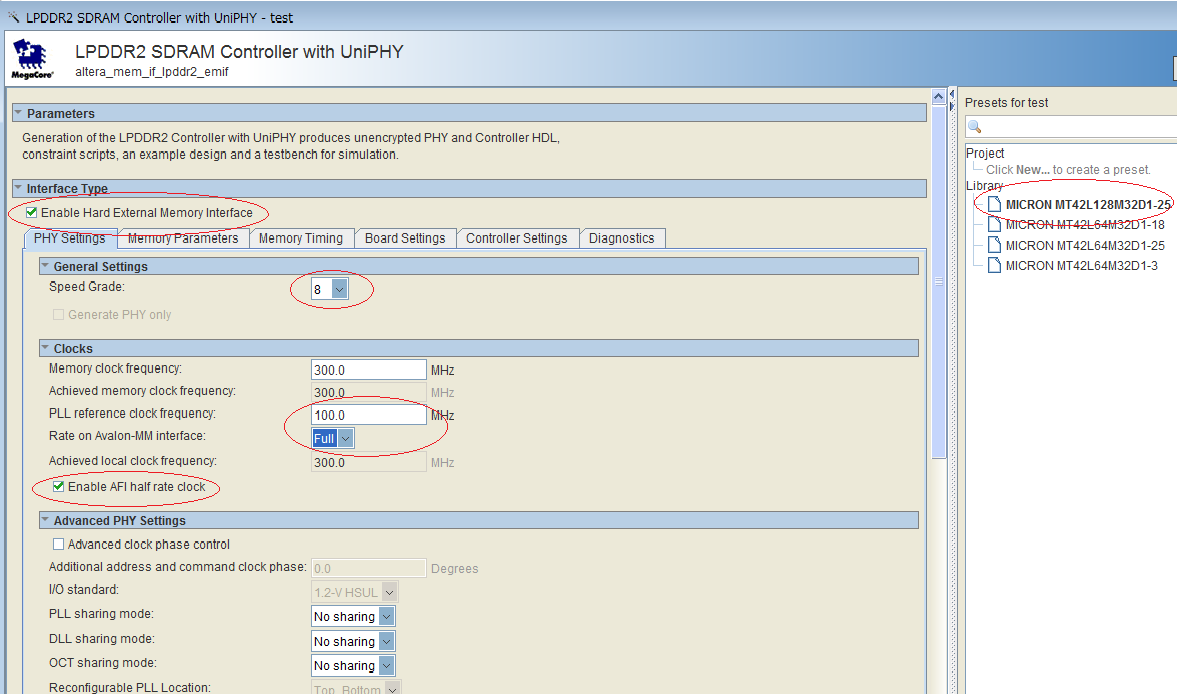

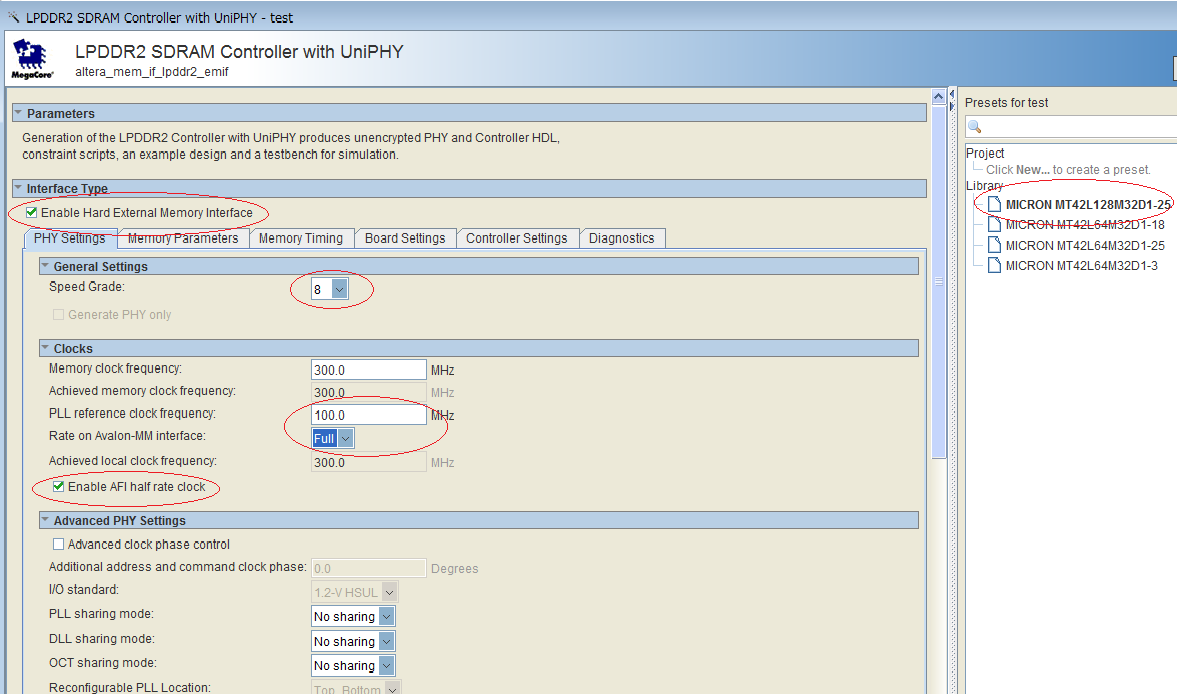

表示された設定画面を次のように変更します。

これだけ変更したら、Finishボタンをクリックして制御コアを生成します。

LPDDR2制御コアを生成すると、xxxx_pin_assignments.tcl ファイルも自動生成されています。

製品添付のサンプルFPGAプロジェクトで提供しているFPGAピンアサイン用のTCLを実行してピンアサインした後、上記のxxxx_pin_assignments.tcl を実行すると、LPDDR2インタフェース用のピン定義が正しくできます。