検索

Contact

PLLのダイナミック位相調整方法

USB経由で簡単に位相調整を行うことができます。

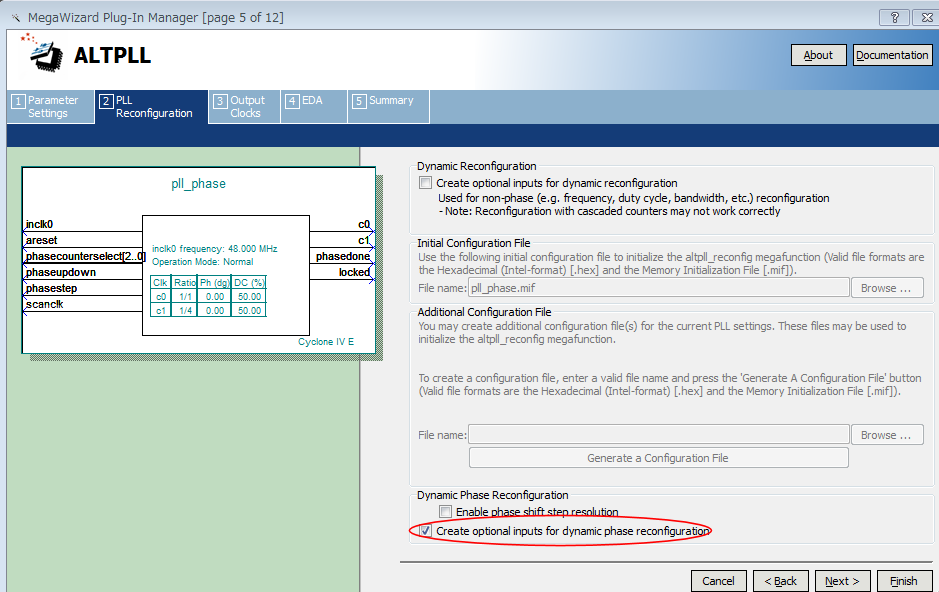

PLLダイナミック位相調整機能を利用するためには、”ALTPLL”IPをMegawizardで生成する際に、5/12ページ目で"Create optional inputs for dynamic phase reconfiguration"のオプションにチェックを入れてください。

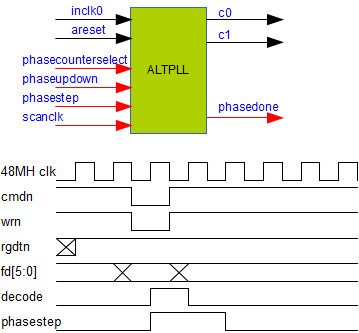

これにより生成される信号線は以下の通り。

1. scanclk : ボード上の48MHzを使うと便利です

2. phasestep : scanclk2個分のパルス幅を与える度に位相調整できます

3. phasecounterselect[2:0] : 調整したいpll出力を選択します

4. phaseupdown :1で進み、0で遅れます

5. phasedone :位相調整が正しくできれば1クロック幅のLowパルスが出力されます

【PLLの制御】

ボードの制御ソフトRefApp7のレジスタ操作により位相調整が簡単にできます。

例えばレジスタNo.2に、位相調整を行うPLL出力の設定と、位相の進み/遅れを設定し、レジスタNo.8をWRクリックする度に位相を進めまたは遅らせることができます。

レジスタNo.2 [7]ビットに、phaseupdown、[2:0]ビットにphasecounterselectをアサインした場合、レジスタNo.2の設定値"82"は、pll出力c0に対して位相を進めます。"02"ならc0出力は遅れます。

phasecounterselectの設定値詳細は、アルテラ社資料のtable5-10を参照してください。

サンプルFPGA回路を利用する前提では、scanclkに48MHzを与え、phasecounterselectとphaseupdownにはレジスタアクセス(No.2)により設定値を与えることができます。

phasestepは48MHzクロック2個分の幅が必要なので、この信号だけ新しく生成します。

例えば、レジスタNo.8をWRしたときに位相調整が行われるようにするには、通常のレジスタアクセス回路を組むように、cmdn=0,wrn=0,rgdtn=1の条件でfd[5:0](レジスタNo.)をデコードします。fd[5:0]の値が"08"になった条件で、パルスを生成し、それを48MHzクロック2個分に伸張するだけです。

この信号がphasestepになります。制御アプリRefApp7からレジスタNo.8にWR(データは不問)するだけで、位相調整ができるようになります。