USBからDCMの位相調整ポートを簡単に制御できます。

USBからレジスタ・アクセスを利用して、DCMが出力するクロックの位相調整をするためには、CoreGenertaorのClocking Wizard(v3.6)を利用します。

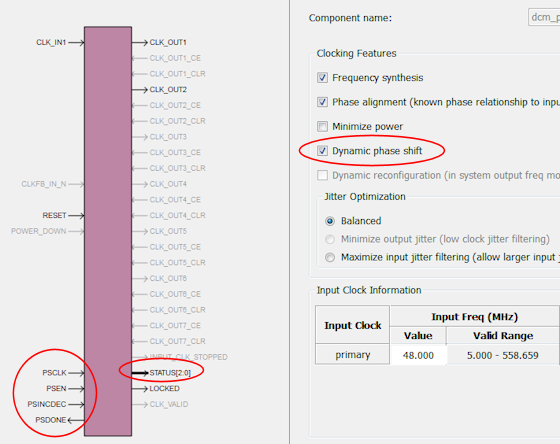

下図は1ページ目の設定画面の一部です。□Dynamic Phase Shiftをチェックすると、DCMシンボルの左下に PSCLK, PSEN, PSINCDEC PSDONEポートができます。

また、設定画面3ページ目で □STATUS をチェックすると、STATUS[2:0]ポートができます。

位相調整に必須の信号は、PSCLK、PSEN、PSINCDEC です。

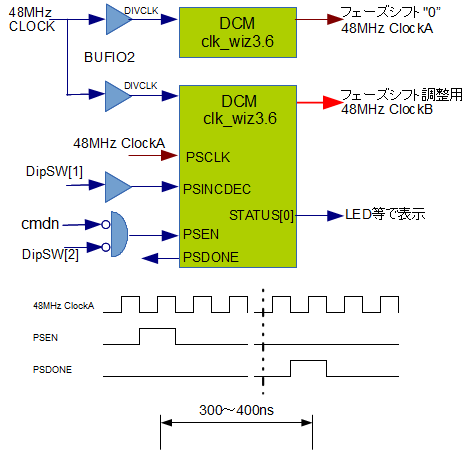

SX-Card6サンプルFPGA回路では、48MHzを CLK_IN1ポートに入力しているので、このクロックから生成されるCLK_OUT1出力クロックとCLK_OUT2出力クロックの位相が調整できます。

USB-IF回路では48MHzクロックに同期した制御線を使用しているので、PSCLK=48MHzクロック、PSEN(反転したcmdn信号)、PSINCDEC(オンボードのディップスイッチでOn/Off切り換え)を接続し、RefApp7のレジスタ操作画面で、「Write」ボタンをクリックすれば、クロックの位相調整が簡単にできます。

(RefApp7については、こちらのページを参照してください)

STATUS信号は、STATUS[0]にオーバーフロー機能があります。これ以上位相調整ができないときにHレベルになります。

SX-Card6 サンプルFPGA回路を利用したときの一例です。 48MHzクロックをフェーズシフトさせるために、新たにDCMを1個追加しています。これにより、位相調整なしの48MHzと位相調整後の48MHzを比較できます。

USB制御ICから受信するcmdn(コマンド信号)を利用すれば、特に回路を組む必要もありません。 RefApp7制御ソフトウエアの「レジスタ操作」画面で、どのレジスタでも良いので「WR」ボタンをクリックするだけで、位相調整ができます。

1回の位相調整ステップは約400ns以下で完了します。

調整量は 48MHzクロックの場合 ±178ステップです。 1ステップはmin.10ps-max.40psです。

1ステップ=40psとした場合、178ステップで 7.12ns 調整可能です

詳細は、Xilinx社のUG382 p.65を参照してください。